## ALTERA MAXPLUS GUIDANCE SIMPLIFIEE

### **PRESENTATION**

ALTERA MAX+PLUS est un outil de développement permettant de concevoir des circuits programmables. Les 4 grandes étapes de la conception d'un circuit programmable peuvent être effectuées avec MAX+PLUS:

- SAISIE (GRAPHIQUE, TEXTUELLE ou CHRONOGRAMME)

- COMPILATION

- SIMULATION VERIFICATION

- DEFINITION DES BROCHES E /S

- PROGRAMMATION DU CIRCUIT INTEGRE

### **UTILISATION**

Lancer le logiciel (ICONE BUREAU ou MENU DEMARRER) Aucun Nom de Projet ne doit apparaître dans le bandeau bleu du Haut de l'écran

#### **MENU FILE**

**PROJECT** NAME (ou choix dans la liste pour ouvrir un projet en cours)

Dans la fenêtre taper un nom ( $\underline{8}$  lettres maxi sans caractères spéciaux)

et choisir le disque et le répertoire de travail

Le nom et le chemin apparaissent dans le bandeau bleu

Important : en cas de changement de fichier faire menu File Project : Set Project to current File

## 1 \* La saisie graphique

(Au cours de ce travail ne pas oublier de faire des sauvegardes régulières.)

si vous changer de fichier vérifier toujours le nom du projet et du fichier dans le bandeau bleu en cas de problème : <u>menu File Project : Set Project to current File</u>

Ouvrez l'éditeur graphique (MENU <u>M</u>AX+plus II Graphic Editor), une fenêtre apparaît (vous pouvez la placer en plein écran)

**1.1 Appelez les composants** avec **le MENU Symbol/Enter symbol** ou en **cliquant deux fois** sur le bouton de gauche de la souris n'importe où dans la fenêtre graphique. La fenêtre des bibliothèques apparaît :

Les bibliothèques importantes à votre disposition sont :

- ⇒ votre propre bibliothèque utilisateur qui contient vos symboles déjà créés.

- ⇒ la bibliothèque de primitives PRIM pour les éléments logiques de base (opérateurs booléens, bascules, broches d'entrée et de sortie,...)

- ⇒ la bibliothèque de macrofonctions MF (circuits TTL, MUX, compteurs,...)

- ⇒ la bibliothèque de macrofonctions paramétrables MEGA LPM

répertoire : (en général *maxplus2\max2lib\mf*, éventuellement *maxplus2\maxlib\prim* ou *maxplus2\max2lib\mega lpm*).

Note : Si vous utilisez un symbole crée par l'utilisateur (ex : 4013) il doit être présent dans votre répertoire de travail (ex : 4013.GDF et 4013.SYM)

Utilisez les **primitives INPUT et OUTPUT** pour les broches d'entrée et de sortie. L'édition du nom se fait en cliquant 2 fois avec le bouton de gauche de la souris dans la zone de texte.

1.2 Reliez les composants par des équipotentielles. Sélectionnez dans la boite d'outil à gauche

l'outil tracé de lignes angle droit) Utiliser l'outil ZOOM si besoin

NOTES : Si le point de départ ou d'arrivée du fil se trouve sur un autre fil, une jonction symbolisée par une boule noire est créée.

#### 1.3 Sauvez MENU File save

Donnez un nom au circuit s'il s'agit de la première saisie.

Le fichier est sauvegardé avec l'extension .GDF

2 \* COMPILATION FONCTIONNELLE (en cas de problème : menu File Project : Set Project to current File

Cette compilation ne tient pas compte du cicuit de destination et est purement fonctionnelle

MENU MAX+plus II COMPILER

Avant d'appuyer sur START : MENU PROCESSING

COCHER FUNCTIONAL SFN EXTRACTOR

Si tout est correct: 0 errors

### **3 \* PREPARATION DE LA SIMULATION**

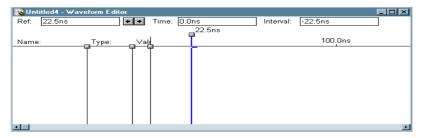

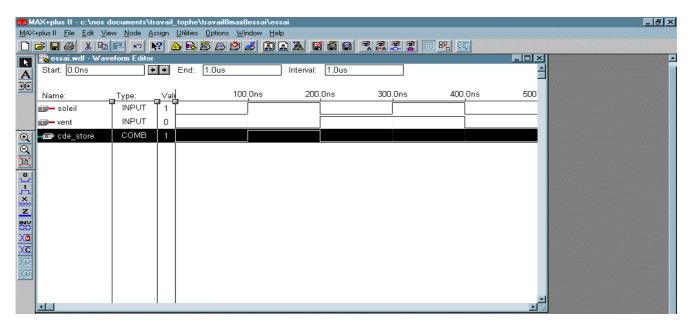

### MENU MAX+plus II WAVEFORM EDITOR

Demandez l'affichage des chronogrammes des signaux désirés avec le

#### MENU Node/Enter Nodes from SNF

Cliquer ensuite sur "List", les entrées et les sorties apparaissent alors dans la fenêtre de gauche.

Les signaux qui seront transférés dans la fenêtre de droite seront alors visualisés dans l'éditeur de chronogrammes.

NOTE :Les signaux peuvent être groupés avec **Node/Enter group** après avoir sélectionner dans la colonne de gauche les noms des signaux à regrouper. Dans la boîte de dialogue, il est possible d'indiquer la représentation du groupe, qui peut être en **binaire**, octal, **décimal ou héxadécimal.**

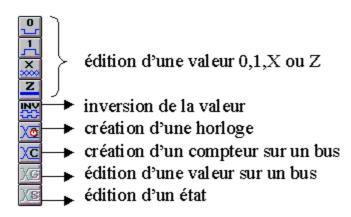

Editez les chronogrammes des signaux d'entrée. plusieurs possibilités :

En sélectionnant l'icône : et en se déplaçant dans le chronogramme du signal à modifier, ceci modifie le niveau logique à chaque pas de grille parcouru.

En sélectionnant l'icône et en se déplaçant dans le chronogramme du signal à modifier de façon à le électionner, le signal sélectionné est modifié en fonction de l'outil choisi :

#### NOTE:

Il est nécessaire d'adapter le pas de grille à l'application :

Le pas de grille est éditable dans **Options/Grid size**.

La fenêtre de simulation qui est de 1uS par défaut, peut être augmentée par le MENU File/End Time.

Si Options/Snap to grid est activé, les changements d'état se feront sur les pas de grille

En cliquant dans la colonne des noms, à gauche, toute la trace est sélectionnée.

Sauvegardez le fichier ainsi créé par le File/Save. Extension .GDF

#### 4 \* SIMULATION

#### MENU MAX+plus II SIMULATEUR

Cliquez sur "start".

Le simulateur calcule alors les chronogrammes des signaux de sorties qui sont mis à jour automatiquement dans le fichier de chronogrammes.

Analysez le fichier de chronogrammes pour vérifier que les chronogrammes des sorties calculés par le simulateur sont conformes à la spécification.

#### **5 \* PROGRAMMATION DU CIRCUIT**

Il faut d'abord recompiler en fonction du circuit de destination

MENU ASSIGN DEVICE et choisir Famille MAX700S device EPM7128SLC84-7

MENU MAX+II COMPILER

Avant d'appuyer sur START : MENU PROCESSING

COCHER TIMING SFN EXTRACTOR

(si la case est grisée décocher la ligne FONCTIONAL SFN EXTRACTOR)

Cliquer sur START cette fois la compilation a 6 étapes

Il faut maintenant assigner les broches du circuit

#### MENU MAX+II FLORPLAN

Deux vues sont possibles :

#### **MENU LAYOUT**

- La vue *Device view* qui montre l'affectation des broches sur le boîtier (externe).

- La vue *Lab view* qui montre les cellules logiques internes au composant.

On passe de l'une à l'autre par double clic dans la fenêtre graphique.

Dans la fenêtre Unassigned Nodes , cliquer sur le petit symbole gris à gauche du nom , en maintenant le bouton de la souris enfoncé , faire glisser sur la broche (I/O) choisi .

Voir la page concernant la carte d'essai UP1 pour le repérage des broches .

Elles peuvent être imposées par le professeur

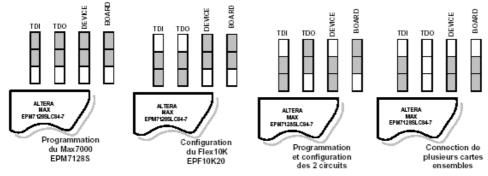

Relier la carte ALTERA au pc sur port imprimante

Programmer:

Vérifier : MENU OPTION HARDWARE ByteBlaster

#### MENU MAX+II PROGRAMMER

Avant START vérifier le nom du fichier envoyé \*\*\*\*\*. POF

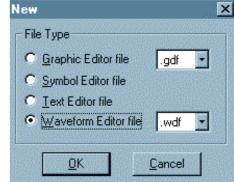

### 6 \* Saisie de description par chronogrammes.

Tout d'abord il faut créer un fichier (ou par Menu → File Open)

et préciser que c'est un fichier waveform (extension.wdf) :

On obtient la même fenêtre que le simulateur.

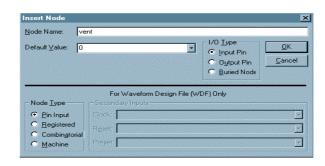

Il faut maintenant nommer les entrées et les sorties du projet par la commande insert node .

Champ à compléter

Champ à compléter

Puis "dessiner" les chronogrammes des E/S avec les commandes ou les icônes du bord gauche de l'écran.

Le projet doit être compilé (voir phase 4) et sauvegardé en tant que symbole : File →create default symbol.

Le symbole ainsi obtenu doit être insérer dans un fichier graphique (extension .gdf) puis recompiler, assigner pour pouvoir programmer le circuit.

## 7\* FICHIERS GENERES

Le tableau suivant indique les fichiers générés par les différentes étapes de conception sous MAX+plus II . Les étapes effectuées automatiquement par l'outil MAX+PLUSII sont indiqués par AUTO. Un fichier au format textuel est indiqué par ASCII.

| ETAPE         | SOUS ETAPE                                          | AUTO | FICHIER GENERE                                                   | ASCII |

|---------------|-----------------------------------------------------|------|------------------------------------------------------------------|-------|

| SAISIE        | saisie graphique                                    |      | <circuit>.gdf</circuit>                                          |       |

|               | saisie textuelle en AHDL                            |      | <circuit>.tdf</circuit>                                          | OUI   |

|               | saisie textuelle en VHDL                            |      | <circuit>.vhd</circuit>                                          | OUI   |

|               | génération du symbole                               | OUI  | <circuit>.sym</circuit>                                          |       |

| COMPILATION   | assignation des contraintes (e.g brochage)          |      | <circuit>.acf</circuit>                                          | OUI   |

|               | génération de fichier résultat (comp. temporelle)   | OUI  | <circuit>.rpt</circuit>                                          | OUI   |

|               | génération d'une netlist ALTERA                     | OUI  | <circuit>.snf</circuit>                                          |       |

|               | génération d'une netlist VHDL                       | OUI  | <circuit>.vho</circuit>                                          | OUI   |

|               | génération de fichier assembleur (comp. temporelle) | OUI  | MAX : <circuit>.pof<br/>FLEX : <circuit>.sof</circuit></circuit> |       |

| VERIFICATION  | édition des chronogrammes de simulation             |      | <circuit>.scf</circuit>                                          |       |

|               | simulation                                          | OUI  | <circuit>.scf avec sorties</circuit>                             |       |

|               | analyse de timings                                  | OUI  |                                                                  |       |

| PROGRAMMATION |                                                     | OUI  |                                                                  |       |

## **8\* REMARQUES SUR l'INSTALLATION**

Vous pouvez récupérer logiciel ALTERA MAX+Plus II sur le site <a href="https://www.altera.com">www.altera.com</a> ( taille 48 Mo)

ou le graver sur le poste 3D répertoire CDALTERA (48 Mo + quelques documents en français)

Pour avoir une licence (Gratuite) connectez vous à : http://www.altera.com/support/licensing/lic-university.html

Il faudra donner votre numéro de disque dur et une adresse Email

Après quelques minutes vous recevez dans votre boite aux lettres un fichier license.dat (300 octets) Que vous placez dans le répertoire ou vous avez installé le logiciel

Validation du logiciel:

Menu OPTION LICENSE SETUP

Avant la première utilisation

Menu Option Preferences : décocher la case : automaticly load last project at start up

Menu Option Users Libririe definir le chemin Altera Max+

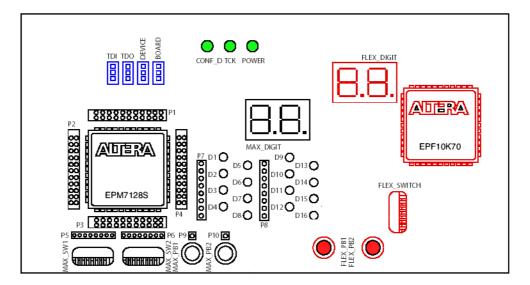

## 9. la carte UP1.

## 9.1 Presentation

En bleu, les cavaliers de configuration. En rouge, tout ce qui concerne le FLEX10K. En vert, les leds de signalisation. En noir, tout ce qui concerne le MAX7000.

Pour utiliser les différentes entrées/sorties de la carte d'évaluation, il faut préciser le numéro des broches auxquelles elles sont reliées. Pour ce faire il suffit d'affecter le numéro de la broche à l'entrée ou la sortie du circuit logique programmable.

# 9.2. Cavaliers de configuration.

Suivant l'utilisation souhaitée de la carte de développement, les cavaliers se trouvant au dessus du circuit MAX7000 doivent être configurés comme indiqué ci-dessous (les zones grisées représentent les bornes en contact).

## 9.3. Circuit FLEX 10K70RC240-4.

**Boutons poussoirs : (Action = niveau logique 0)**

PB1: broche 28 PB2: broche 29

| Interrupteur DIP : SW1 (ON = niveau |

|-------------------------------------|

| logique 0):                         |

| 1 : broche 41                       |

| 2 : broche 40                       |

| 3 : broche 39                       |

| 4 : broche 38                       |

| 5 : broche 36                       |

| 6 : broche 35                       |

| 7 : broche 34                       |

| 8 : broche 33                       |

|                                     |

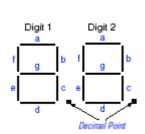

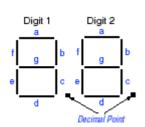

## Afficheurs 7 segments (allumés au niveau bas)

| Display Segment | Pin for Digit 1 | Pin for Digit 2 |  |  |  |

|-----------------|-----------------|-----------------|--|--|--|

| a               | 6               | 17              |  |  |  |

| ь               | 7               | 18              |  |  |  |

| С               | 8               | 19              |  |  |  |

| d               | 9               | 20              |  |  |  |

| Φ               | 11              | 21              |  |  |  |

| f               | 12              | 23              |  |  |  |

| g               | 13              | 24              |  |  |  |

| Decimal point   | 14              | 25              |  |  |  |

Signal d'horloge: On dispose d'un signal d'horloge à 25,175 MHz affecté à la broche 91.

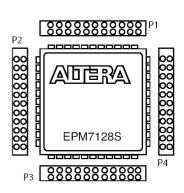

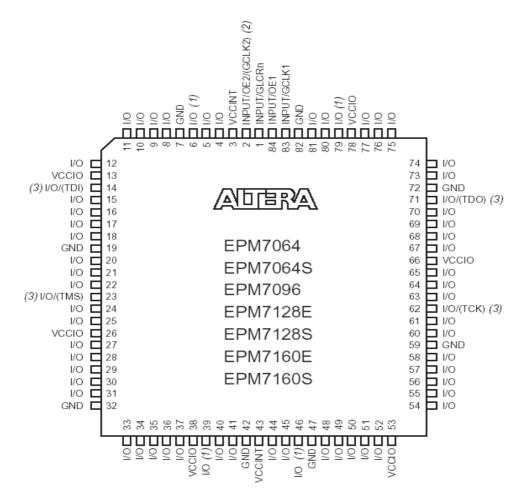

# 9.4. Circuit MAX 7128 SLC 84 - 7

# 4. Circuit MAX 7128 SLC 84 - 7

## Afficheurs 7 segments (allumés au niveau bas)

| Display Segment | Pin for Digit 1 | Pin for Digit 2 |  |

|-----------------|-----------------|-----------------|--|

| a               | 58              | 69              |  |

| b               | 60              | 70              |  |

| С               | 61              | 73              |  |

| d               | 63              | 74              |  |

| 9               | 64              | 76              |  |

| f               | 65              | 75              |  |

| g               | 67              | 77              |  |

| Decimal point   | 68              | 79              |  |

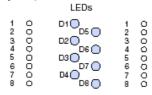

#### LEDS (allumée par un niveau logique 0)

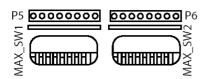

Interrupteurs DIP: SW1 et SW2 (ON = niveau logique 0)

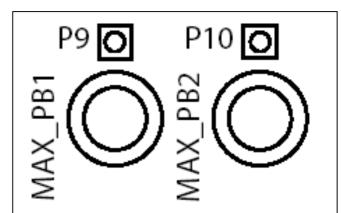

Boutons poussoirs

(Action = niveau logique 0)

PB1 : raccord libre P9 PB2 : raccord libre P10

#### Signal d'horloge:

On dispose d'un signal d'horloge à 25,175 MHz affecté à la broche 83.

#### Le MAX 7128 SLC 84 - 7

4 connecteurs P1, P2, P3 et P4 permettent son raccord (inside = coté composant).

| P1      |        | P2      |        | P3      |        | P4      |        |

|---------|--------|---------|--------|---------|--------|---------|--------|

| Outside | Inside | Outside | Inside | Outside | Inside | Outside | Inside |

| 75      | 76     | 12      | 13     | 33      | 34     | 54      | 55     |

| 77      | 78     | 14      | 15     | 35      | 36     | 56      | 57     |

| 79      | 80     | 16      | 17     | 37      | 38     | 58      | 59     |

| 81      | 82     | 18      | 19     | 39      | 40     | 60      | 61     |

| 83      | 84     | 20      | 21     | 41      | 42     | 62      | 63     |

| 1       | 2      | 22      | 23     | 43      | 44     | 64      | 65     |

| 3       | 4      | 24      | 25     | 45      | 46     | 66      | 67     |

| 5       | 6      | 26      | 27     | 47      | 48     | 68      | 69     |

| 7       | 8      | 28      | 29     | 49      | 50     | 70      | 71     |

| 9       | 10     | 30      | 31     | 51      | 52     | 72      | 73     |

| 11      | Χ      | 32      | Х      | 53      | Х      | 74      | Х      |